Tin Công Nghệ

Biểu đồ Intel về chip bóng bán dẫn nghìn tỷ

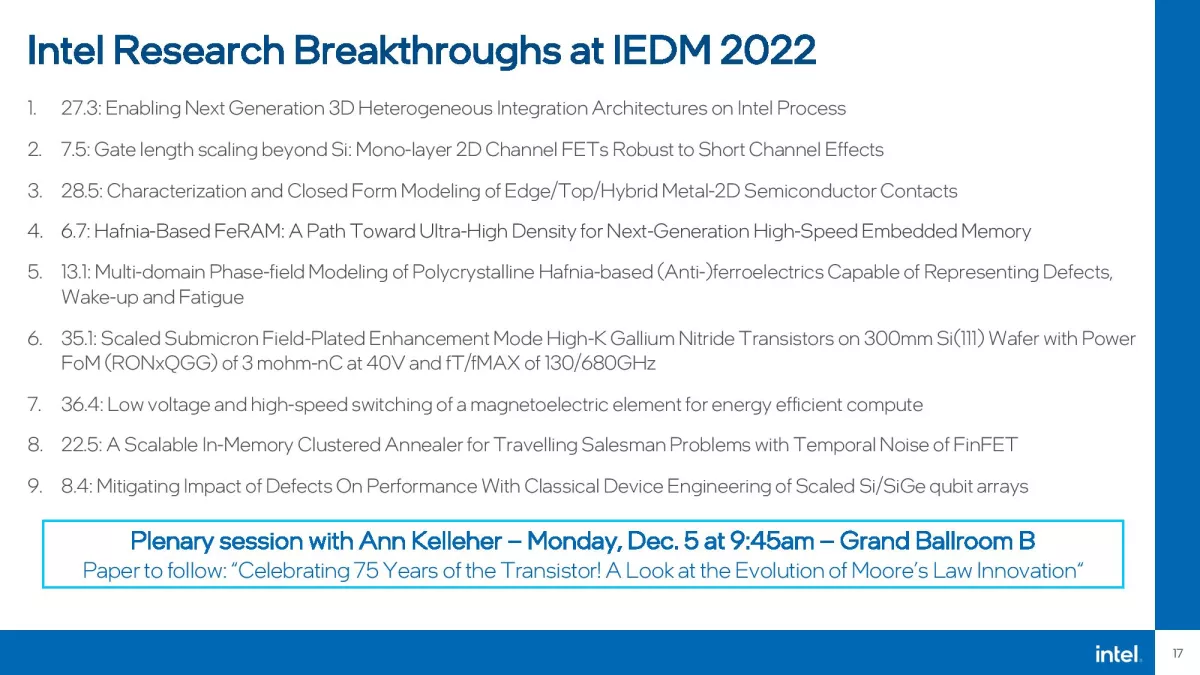

Intel đã công bố 9 tài liệu nghiên cứu tại IEDM 2022 đặt nền móng cho các thiết kế chip trong tương lai khi công ty mong muốn thực hiện lời hứa phát triển bộ vi xử lý với hơn một nghìn tỷ bóng bán dẫn vào năm 2030.

Mục lục

Intel đặt nền tảng ban đầu cho các công nghệ tương lai

Nghiên cứu bao gồm các vật liệu 2D mới cho bóng bán dẫn, công nghệ đóng gói 3D mới giúp thu hẹp khoảng cách về hiệu suất và năng lượng giữa các bộ xử lý chiplet và bộ xử lý một khuôn đến một phạm vi gần như không thể nhận thấy, các bóng bán dẫn ‘không quên’ khi ngắt nguồn và các bộ nhớ nhúng có thể xếp chồng trực tiếp lên trên các bóng bán dẫn và lưu trữ nhiều hơn một bit trên mỗi ô, trong số những đổi mới khác.

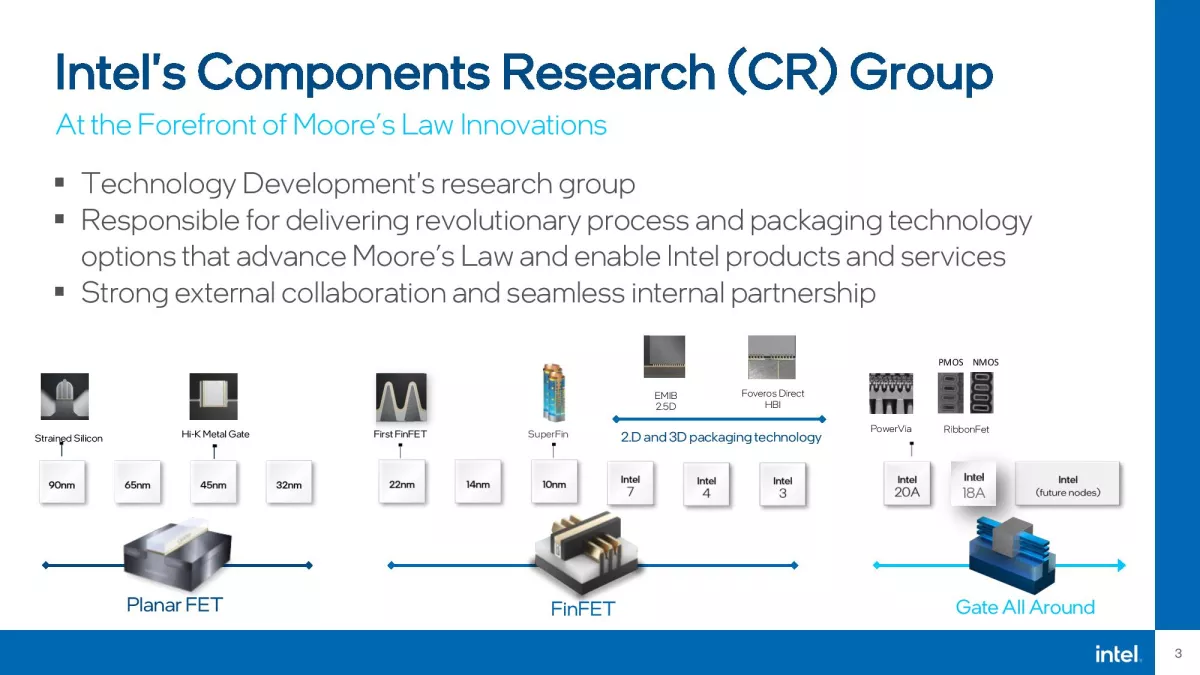

Nhóm Nghiên cứu Linh kiện (CR) của Intel đặt nền tảng ban đầu cho các công nghệ tương lai của công ty, nhưng không phải tất cả các sáng kiến này đều dẫn đến các sản phẩm được tung ra thị trường. Những sản phẩm được tung ra thị trường thường sẽ xuất hiện sau 5 đến 10 năm.

Nhóm này có thành tích đáng kinh ngạc về những đổi mới đã được đưa ra thị trường, chẳng hạn như FinFET, đã cách mạng hóa thiết kế bóng bán dẫn cho toàn ngành, silicon căng, cổng kim loại Hi-K, và nhiều sản phẩm khác. Intel đã có một số công nghệ khác trên lộ trình của mình, bao gồm bóng bán dẫn RibbonFET Gate All Around (GAA) , phân phối điện năng mặt sau PowerVia, EMIB và Foveros Direct, tất cả đều đến từ nhóm nghiên cứu này.

Cpu intel cũ mà bạn quan tâm được bán tại đây

Nhóm đã gửi chín tài liệu nghiên cứu tại Cuộc họp thường niên lần thứ 68 về thiết bị điện tử quốc tế của IEEE năm nay và dưới đây, chúng tôi sẽ đề cập chi tiết hơn một chút về một số tài liệu đó. Tuy nhiên, Intel vẫn chưa trình bày các bài báo tại hội nghị, vì vậy đây là phạm vi bao quát của các chủ đề.

Tốc độ tăng mật độ bóng bán dẫn tiếp tục gần như phù hợp với Định luật Moore, nhưng tính kinh tế của các con chip ngày nay không cải thiện với tốc độ tương tự — giá mỗi bóng bán dẫn đang tăng lên khi chúng ta chuyển sang các nút dày đặc hơn. Ngoài ra, khả năng mở rộng kém của một số thành phần chip, như tín hiệu tương tự và bộ đệm, càng làm phức tạp thêm vấn đề. Do đó, ngành công nghiệp đang chuyển sang thiết kế dựa trên chiplet cho các chip hiệu suất cao.

Mục tiêu tạo trên một quy trình tiên tiến nhất

Mục tiêu quan trọng nhất của bất kỳ thiết kế dựa trên chiplet nào là bảo toàn các thuộc tính tốt nhất về mức tiêu thụ điện năng và hiệu suất (độ trễ, băng thông) của các đường dẫn dữ liệu bên trong bộ xử lý nguyên khối một khuôn trong khi khai thác lợi ích kinh tế của việc sử dụng phương pháp dựa trên chiplet , chẳng hạn như năng suất tăng lên từ các khuôn nhỏ hơn được chế tạo trên một quy trình tiên tiến nhất và khả năng sử dụng các nút cũ hơn, rẻ hơn cho một số chức năng khác có mật độ cải thiện ít hơn.

Do đó, chiến trường giành ưu thế về chất bán dẫn đang chuyển từ tốc độ của bóng bán dẫn sang hiệu suất của các kết nối, với các công nghệ mới như bộ xen kẽ silicon (EMIB) và kỹ thuật liên kết lai đang đi đầu để cải thiện tính kinh tế.

Mua mainboard cũ phù hợp với chip Intel tại Khoserver

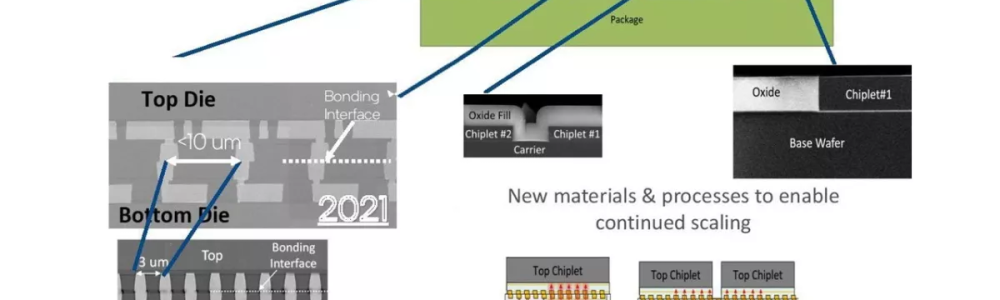

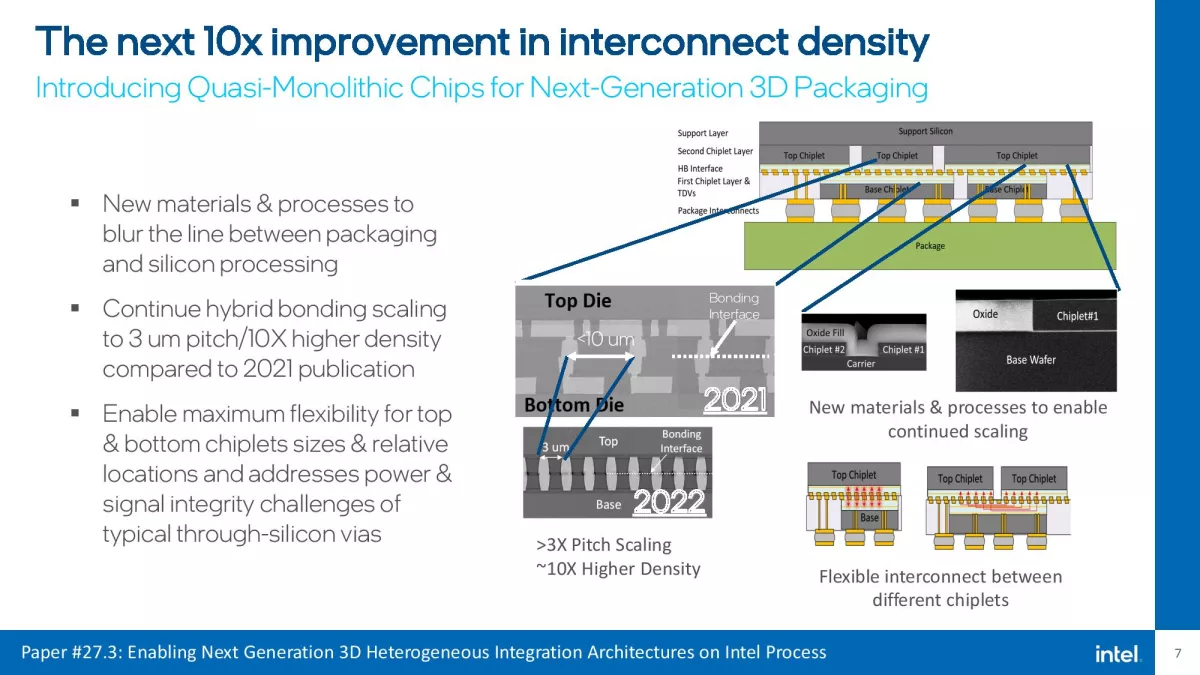

Tuy nhiên, những cách tiếp cận này vẫn dẫn đến sự đánh đổi không thể tránh khỏi về hiệu suất, điện năng và chi phí, điều mà công nghệ đóng gói 3D ‘Quasi-Monolithic Chips’ (QMC) mới của Intel sẽ giải quyết. Đúng như tên gọi, QMC của Intel nhằm mục đích cung cấp các đặc điểm gần giống như các kết nối được tích hợp ngay trong một khuôn duy nhất.

Con đường dẫn đến cải tiến 100X chỉ trong vài năm

QMC là một kỹ thuật liên kết lai mới có bước nhảy phụ 3 micron và mang lại hiệu quả sử dụng năng lượng và mật độ hiệu suất tăng gấp 10 lần so với nghiên cứu mà Intel đã đệ trình tại IEDM năm ngoái. Bài báo trước đó đề cập đến một cách tiếp cận với bước sóng 10 micron, đây đã là một cải tiến gấp 10 lần. Do đó, Intel đã tìm ra con đường dẫn đến cải tiến 100X chỉ trong vài năm, cho thấy công việc của công ty trong lĩnh vực liên kết lai đang tăng tốc nhanh chóng. QMC cũng cho phép nhiều bộ ba được xếp chồng lên nhau theo chiều dọc, như thể hiện trong hình trên.

Bài viết này phác thảo mật độ kết nối đáng kinh ngạc của hàng trăm nghìn kết nối trên một milimet vuông và mức tiêu thụ điện năng (được đo bằng picojoules trên bit – Pj/b) sánh ngang với những gì chúng ta thấy trong bộ xử lý nguyên khối. Ngoài ra, bài báo mới phác thảo một số vật liệu và quy trình mới sẽ được sử dụng để sản xuất các thiết bị như vậy, mở đường cho các thiết bị trong thế giới thực.

Lộ trình quy trình của Intel trong tương lai

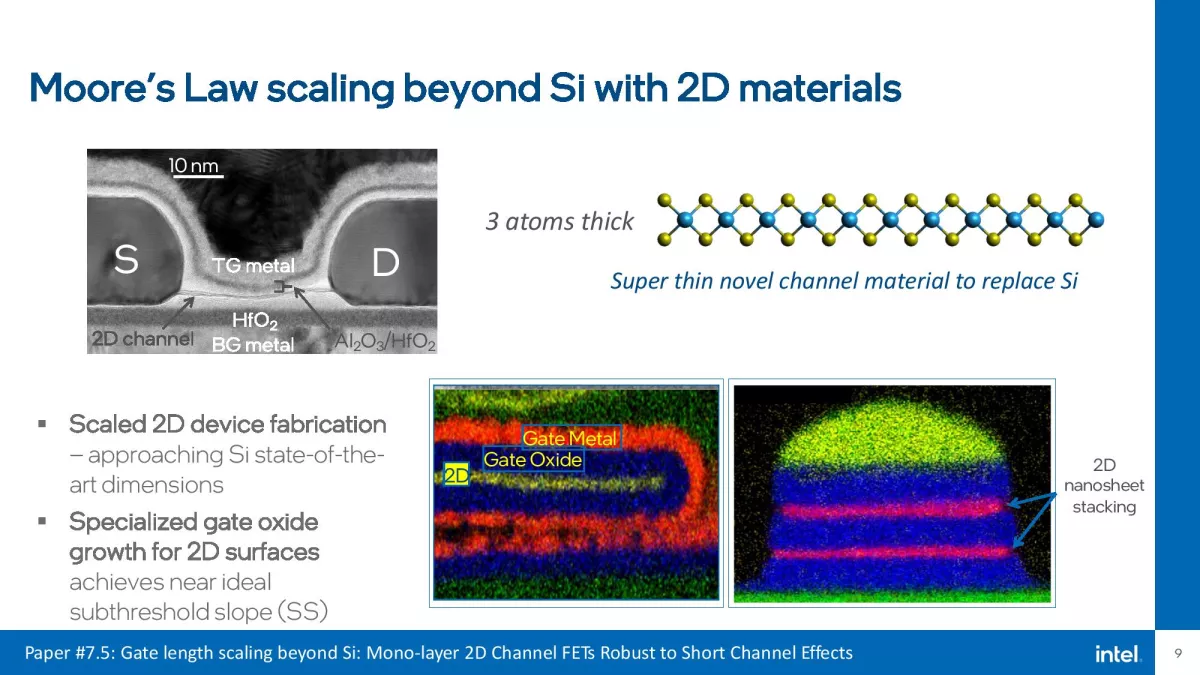

Lộ trình quy trình của Intel đã giảm xuống dưới thang nanomet xuống thang Angstrom và mặc dù các quy ước đặt tên nút từ lâu đã không còn liên quan đến các phép đo vật lý thực tế của các bóng bán dẫn, nhưng rõ ràng sẽ cần một phương pháp hoàn toàn mới để tiếp tục mở rộng quy mô. Hầu hết ngành công nghiệp đang đặt cược vào việc chuyển sang các kênh nguyên tử 2D trong tương lai , nhưng cũng như với tất cả các công nghệ mới, sẽ có nhiều bước để đạt được sự thay đổi triệt để như vậy.

Các vật liệu chip ngày nay, như silicon, bao gồm các tinh thể ba chiều, nghĩa là các nguyên tử được liên kết trong cả ba chiều, do đó đưa ra một giới hạn cơ bản đối với sự co lại. Ngược lại, vật liệu 2D hấp dẫn vì tất cả các nguyên tử được liên kết trong một mặt phẳng, do đó cho phép các tính năng được chế tạo với độ dày chỉ bằng ba nguyên tử.

Mua ổ ssd cũ cho máy chủ của bạn tại đây

Tham gia nghiên cứu của Intel về các vật liệu 2D mà hãng này có thể sử dụng cho các bóng bán dẫn 3D GAA. Để làm mới lại, các thiết kế GAA hiện tại bao gồm các tấm nano silicon nằm ngang xếp chồng lên nhau , với mỗi tấm nano được bao quanh hoàn toàn bởi một cổng. Kỹ thuật ‘cổng tất cả xung quanh’ (GAA) này giúp giảm rò rỉ điện áp ngăn cản việc tắt các bóng bán dẫn. Điều này ngày càng trở thành một vấn đề khi bóng bán dẫn co lại — ngay cả khi cổng bao quanh kênh ở ba phía, như chúng ta thấy với bóng bán dẫn FinFET.

Intel đặt tên cho thiết kế GAA của mình là RibbonFET, hiện đang được lên kế hoạch ra mắt vào nửa đầu năm 2024. Tuy nhiên, việc vượt ra ngoài RibbonFET sẽ đòi hỏi những đổi mới hơn nữa và nghiên cứu 2D này phù hợp với dự luật về lộ trình tiềm năng.

Bài báo của Intel mô tả cấu trúc tấm nano xếp chồng lên nhau Gate All Around (GAA) với các vật liệu kênh (tấm nano/dải nano) có độ dày chỉ bằng ba nguyên tử và có thể hoạt động ở nhiệt độ phòng với dòng rò thấp.

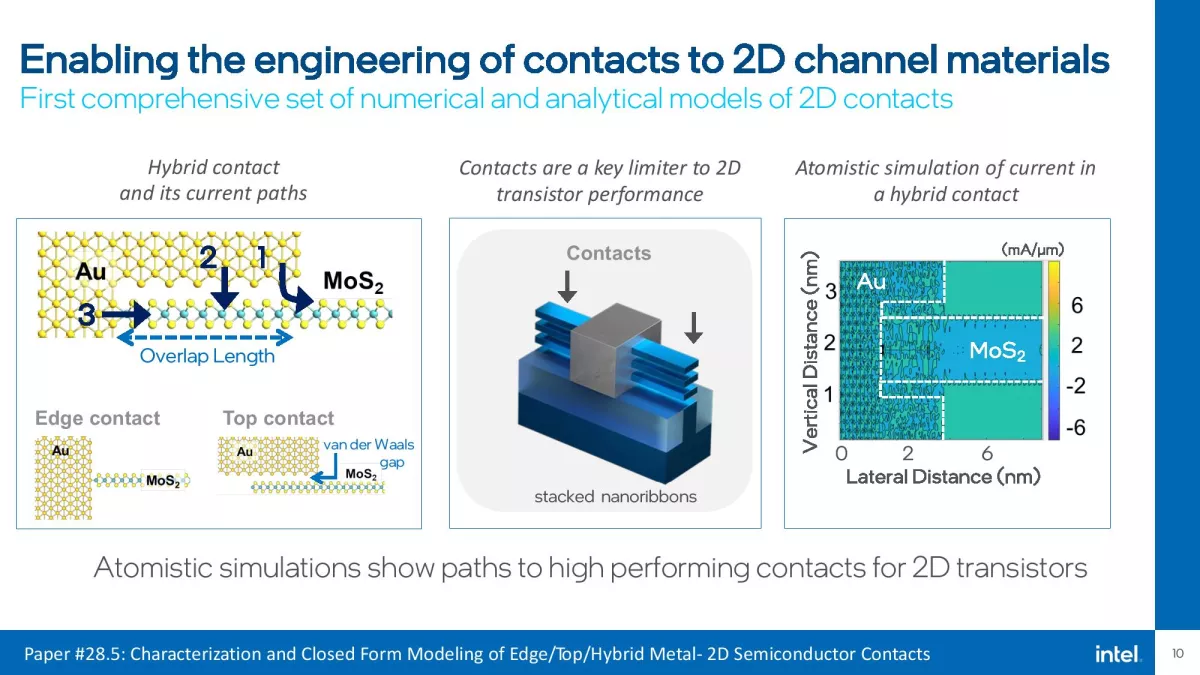

Độ mỏng của vật liệu kênh 2D khiến việc thiết lập kết nối điện với dải nano trở thành một nhiệm vụ khó khăn, vì vậy Intel cũng lập mô hình cấu trúc liên kết tiếp xúc điện cho vật liệu 2D. Đây là một bước quan trọng để hiểu các thuộc tính của vật liệu 2D và cách chúng hoạt động, do đó cho phép công ty lập mô hình chính xác cho các cải tiến tiếp theo.

Bộ nhớ ở mọi dạng là một phần không thể thiếu của điện toán, nhưng nó cũng tiêu tốn nhiều ngân sách năng lượng ở cả cấp độ chip và hệ thống đồng thời là một yếu tố hạn chế đối với hiệu suất.

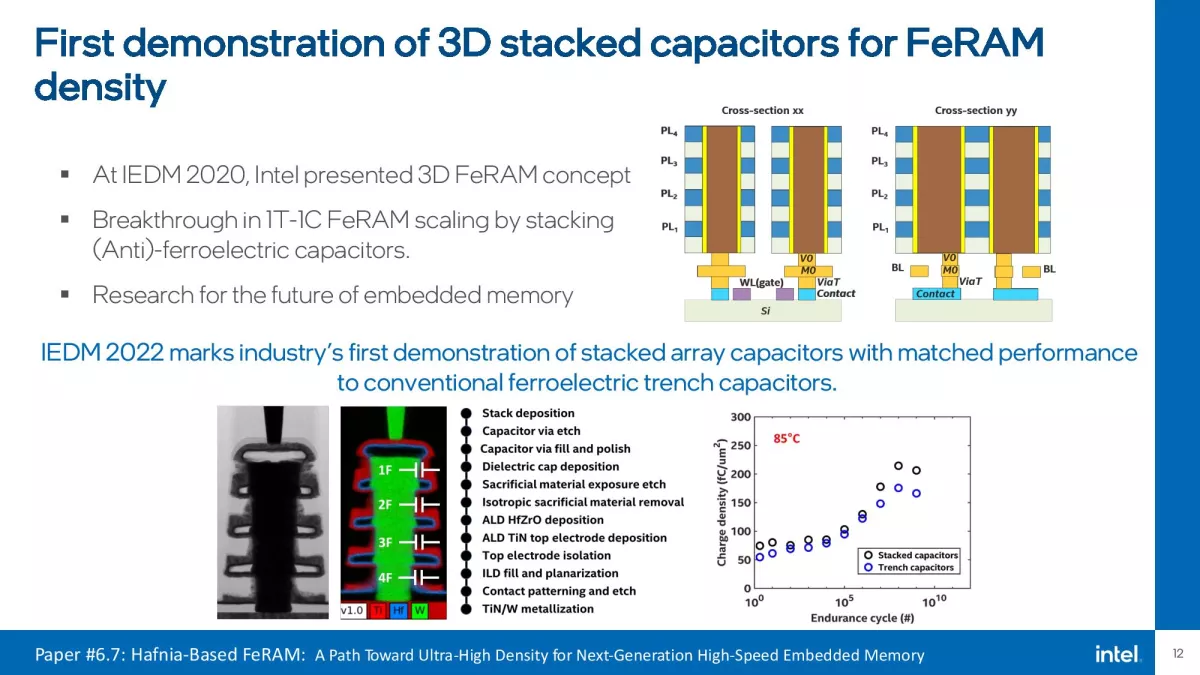

Intel cũng đã tiến hành trình diễn chức năng đầu tiên trên thế giới của bộ nhớ sắt điện xếp chồng 3D. Khía cạnh ấn tượng nhất của công nghệ này là các tụ điện rãnh sắt điện có thể được xếp chồng lên nhau theo chiều dọc trên khuôn logic trên đỉnh các bóng bán dẫn. Điều đó cho phép phân lớp bộ nhớ trên cùng các thành phần logic thay vì ở trong vùng riêng biệt của nó, như chúng ta thấy với các loại bộ nhớ nhúng khác, như SRAM được sử dụng cho bộ đệm L1 và L2.

Nguồn : tomshardware

KhoServer – Kho Máy Chủ Thanh Lý phân phối các dòng máy chủ cũ, workstation cũ, linh kiện máy chủ, thiết bị lưu trữ từ các nhà sản xuất hàng đầu thế giới như: dell, Intel, HP, IBM(Lenovo), Supermicro,…Các thiết bị mạng giá rẻ của Cisco, Juniper, HPE, IBM,… Tất cả đều được nhập khẩu trực tiếp từ nước ngoài, đảm bảo chất lượng và nguồn gốc sản phẩm.

Có thể bạn quan tâm